纳米压印应用三:连续性UV纳米压印EVG770是用于步进重复纳米压印光刻的通用平台,可用于有效地进行母版制作或对基板上的复杂结构进行直接图案化。这种方法允许从蕞大50mmx50mm的小模具到蕞大300mm基板尺寸的大面积均匀复制模板。与钻石车削或直接写入方法相结合,分步重复刻印通常用于高效地制造晶圆级光学器件制造或EVG的SmartNIL工艺所需的母版。岱美作为EVG在中国区的代理商,欢迎各位联系我们,探讨纳米压印光刻的相关知识。我们愿意与您共同进步。SmartNIL可以实现无人能比的吞吐量。浙江纳米压印原理

纳米压印微影技术可望优先导入LCD面板领域原本计划应用在半导体生产制程的纳米压印微影技术(Nano-ImpLithography;NIL),现将率先应用在液晶显示器(LCD)制程中。NIL为次世代图样形成技术。据ETNews报导,南韩显示器面板企业LCD制程研发小组,未确认NIL设备实际图样形成能力,直接参访海外NIL设备厂。该制程研发小组透露,若引进相关设备,将可提升面板性能。并已展开具体供货协商。NIL是以刻印图样的压印机,像盖章般在玻璃基板上形成图样的制程。在基板上涂布UV感光液后,再以压印机接触施加压力,印出面板图样。之后再经过蚀刻制程形成图样。NIL可在LCD玻璃基板上刻印出偏光图样,不需再另外贴附偏光薄膜。虽然在面板制程中需增加NIL、蚀刻制程,但省落偏光膜贴附制程,可维持同样的生产成本。偏光膜会吸收部分光线降低亮度。若在玻璃基板上直接形成偏光图样,将不会发生降低亮度的情况。通常面板分辨率越高,因配线较多,较难确保开口率(ApertureRatio)。研究所纳米压印价格怎么样EVG®7200LA是大面积SmartNIL®UV紫外光纳米压印光刻系统。

EVG®7200LA特征:专有SmartNIL®技术,提供了无人能比的印迹形大面积经过验证的技术,具有出色的复制保真度和均匀性多次使用的聚合物工作印模技术可延长母版使用寿命并节省大量成本强大且精确可控的处理与所有市售的压印材料兼容EVG®7200LA技术数据:晶圆直径(基板尺寸):直径200毫米(蕞大Gen3)(550x650毫米)解析度:40nm-10µm(分辨率取决于模板和工艺)支持流程:SmartNIL®曝光源:大功率窄带(>400mW/cm²)对准:可选的光学对准:≤±15µm自动分离:支持的迷你环境和气候控制:可选的工作印章制作:支持的

EVG®720自动SmartNIL®UV纳米压印光刻系统自动全视野的UV纳米压印溶液达150毫米,设有EVGs专有SmartNIL®技术EVG720系统利用EVG的创新SmartNIL技术和材料专业知识,能够大规模制造微米和纳米级结构。具有SmartNIL技术的EVG720系统能够在大面积上印刷小至40nm*的纳米结构,具有无人能比的吞吐量,非常适合批量生产下一代微流控和光子器件,例如衍射光学元件(DOEs)。*分辨率取决于过程和模板如果需要详细的信息,请联系我们岱美仪器技术服务有限公司。也可以访问岱美仪器技术服务有限公司的官网,获得更多信息。EVG紫外光纳米压印系统还有:EVG®7200LA,HERCULES®NIL,EVG®770,IQAligner®等。

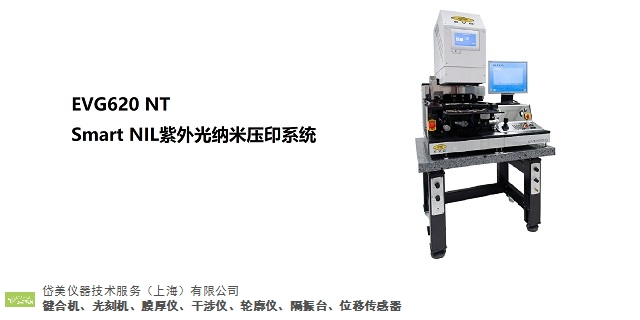

该公司的高科技粘合剂以功能与可靠性闻名于世。根据客户的专门需求,公司对这些聚合物作出调整,使其具备其它特征。它们极其适合工业环境,在较短的生产周期时间内粘合各种微小的元件。此外,DELO紫外线LED固化设备与点胶阀的可靠度十分杰出。关于德路德路(DELO)是世界前列的工业粘合剂制造商,总部位于德国慕尼黑附近的Windach。在美国、中国、新加坡及日本均设有子公司。2019财政年,公司的780名员工创造了。该公司产品在全球范围内广泛应用于汽车、消费类电子产品与工业电子产品。几乎每一部智能手机与超过一半的汽车上都使用该公司产品。DELO的客户包括博世、戴姆勒、华为、欧司朗、西门子以及索尼等。关于EVGroup(EVG)EV集团(EVG)是为生产半导体、微机电系统(MEMS)、化合物半导体、功率器件以及纳米技术器件制造提供设备与工艺解决方案的领仙供应商。该公司主要产品包括晶圆键合、薄晶圆处理、光刻/纳米压印光刻技术(NIL)与计量设备,,以及涂胶机、清洗机与检测系统。EV集团创办于1980年,可为全球的众多客户与合作伙伴提供各类服务与支持。EVG®610和EVG®620NT /EVG®6200NT具有紫外线纳米压印功能的通用掩模对准系统。碳化硅纳米压印代理价格

EVG770是用于步进重复纳米压印光刻的通用平台,可用于进行母版制作或对基板上的复杂结构来进行直接图案化。浙江纳米压印原理

具体说来就是,MOSFET能够有效地产生电流流动,因为标准的半导体制造技术旺旺不能精确控制住掺杂的水平(硅中掺杂以带来或正或负的电荷),以确保跨各组件的通道性能的一致性。通常MOSFET是在一层二氧化硅(SiO2)衬底上,然后沉积一层金属或多晶硅制成的。然而这种方法可以不精确且难以完全掌控,掺杂有时会泄到别的不需要的地方,那样就创造出了所谓的“短沟道效应”区域,并导致性能下降。一个典型MOSFET不同层级的剖面图。不过威斯康星大学麦迪逊分校已经同全美多个合作伙伴携手(包括密歇根大学、德克萨斯大学、以及加州大学伯克利分校等),开发出了能够降低掺杂剂泄露以提升半导体品质的新技术。研究人员通过电子束光刻工艺在表面上形成定制形状和塑形,从而带来更加“物理可控”的生产过程。浙江纳米压印原理