从技术标准化层面看,三维光子芯片多芯MT-FA光互连需建立涵盖设计、制造、测试的全链条规范。在芯片级标准中,需定义三维堆叠的层间对准精度(≤1μm)、铜锡键合的剪切强度(≥100MPa)以及光子层与电子层的热膨胀系数匹配(CTE差异≤2ppm/℃),以确保高速信号传输的完整性。针对MT-FA组件,需制定光纤阵列的端面角度公差(±0.5°)、通道间距一致性(±0.2μm)以及插芯材料折射率控制(1.44±0.01)等参数,保障多芯并行耦合时的光功率均衡性。在系统级测试方面,需建立包含光学频谱分析、误码率测试、热循环可靠性验证的多维度评估体系,例如要求在-40℃至85℃温度冲击下,80通道并行传输的误码率波动不超过0.5dB。当前,国际标准化组织已启动相关草案编制,重点解决三维光子芯片与CPO(共封装光学)架构的兼容性问题,包括光引擎与MT-FA的接口定义、硅波导与光纤阵列的模场匹配标准等。随着1.6T光模块商业化进程加速,预计到2027年,符合三维光互连标准的MT-FA组件市场规模将突破12亿美元,成为支撑AI算力基础设施升级的重要器件。数据中心升级中,三维光子互连芯片可有效解决传统电互连带宽瓶颈问题。光通信三维光子互连芯片生产

从系统集成角度看,多芯MT-FA光组件的定制化能力进一步强化了三维芯片架构的灵活性。其支持端面角度、通道数量、保偏特性等参数的深度定制,可适配不同工艺节点的三维堆叠需求。例如,在逻辑堆叠逻辑(LOL)架构中,上层芯片可能采用5nm工艺实现高性能计算,下层芯片采用28nm工艺优化功耗,MT-FA组件可通过调整光纤阵列的pitch精度(误差<0.5μm)和偏振消光比(≥25dB),确保异构晶片间的光耦合效率超过95%。此外,其体积小、高密度的特性与三维芯片的紧凑设计高度契合,单个MT-FA组件可替代传统多个单芯连接器,将封装体积缩小40%以上,同时通过多芯并行传输降低布线复杂度,使系统级信号完整性(SI)提升20%。这种深度集成不仅简化了三维芯片的散热设计,还通过光信号的隔离特性减少了层间电磁干扰(EMI),为高带宽、低延迟的AI算力架构提供了物理层保障。随着三维芯片向单芯片集成万亿晶体管的目标演进,MT-FA光组件的技术迭代将直接决定其能否突破内存墙与互连墙的双重限制,成为未来异构集成系统的重要基础设施。兰州3D光芯片三维光子互连芯片与光模块协同优化,进一步降低整体系统的能耗水平。

在应用场景层面,三维光子集成多芯MT-FA组件已成为支撑CPO共封装光学、LPO线性驱动等前沿架构的关键基础设施。其多芯并行传输特性与硅光芯片的CMOS工艺兼容性,使得光模块封装体积较传统方案缩小40%,功耗降低25%。例如,在1.6T光模块中,通过将16个单模光纤芯集成于直径3mm的MT插芯内,配合三维堆叠的透镜阵列,可实现单波长200Gbps信号的无源耦合,将光引擎与电芯片的间距压缩至0.5mm以内,大幅提升了信号完整性。更值得关注的是,该技术通过引入波长选择开关(WSS)与动态增益均衡算法,使多芯MT-FA组件能够自适应调节各通道光功率,在40km传输距离下仍可保持误码率低于1E-12。随着三维光子集成工艺的成熟,此类组件正从数据中心内部互联向城域光网络延伸,为6G通信、量子计算等场景提供较低时延、超高密度的光传输解决方案,其市场渗透率预计在2027年突破35%,成为光通信产业价值链升级的重要驱动力。

在AI算力与超高速光通信的双重驱动下,多芯MT-FA光组件与三维芯片互连技术的融合正成为突破系统性能瓶颈的关键路径。作为光模块的重要器件,MT-FA通过精密研磨工艺将光纤阵列端面加工为特定角度,结合低损耗MT插芯实现多路光信号的并行传输。其技术优势体现在三维互连的紧凑性与高效性上:在垂直方向,MT-FA的微米级通道间距与硅通孔(TSV)技术形成互补,TSV通过深硅刻蚀、原子层沉积(ALD)绝缘层及电镀铜填充,实现芯片堆叠层间的垂直导电,而MT-FA则通过光纤阵列的并行连接将光信号直接耦合至芯片光接口,缩短了光-电-光转换的路径;在水平方向,再布线层(RDL)技术进一步扩展了互连密度,使得MT-FA组件能够与逻辑芯片、存储器等异质集成,形成高带宽、低延迟的光电混合系统。以800G光模块为例,MT-FA的12芯并行传输可将单通道速率提升至66.7Gbps,配合TSV实现的3D堆叠内存,使系统带宽密度较传统2D封装提升近2个数量级,同时功耗降低30%以上。三维光子互连芯片具备良好的垂直互连能力,有效缩短了信号传输路径,降低了传输延迟。

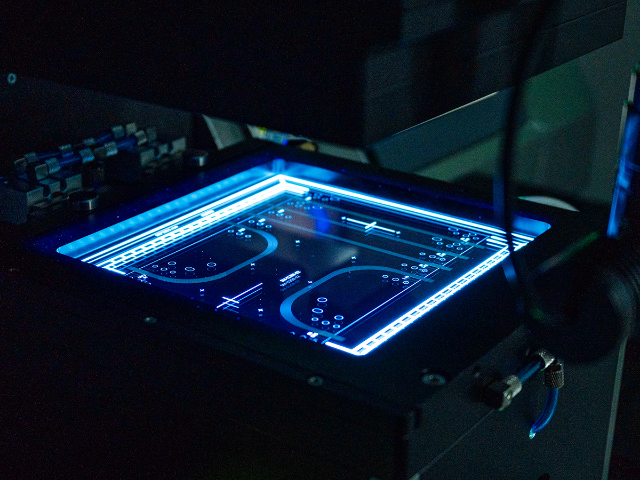

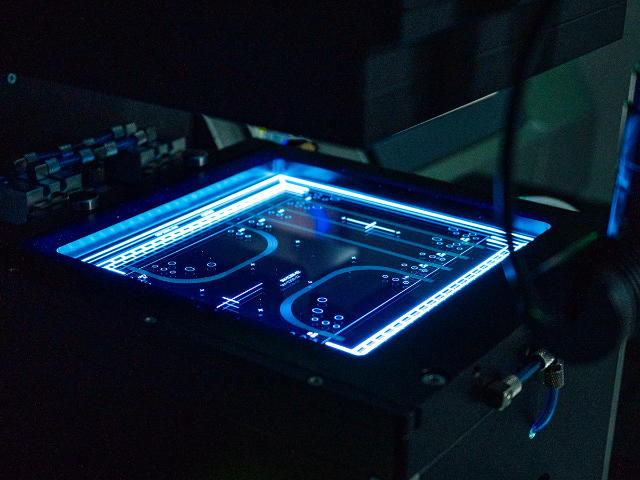

三维集成对高密度多芯MT-FA光组件的赋能体现在制造工艺与系统性能的双重革新。在工艺层面,采用硅通孔(TSV)技术实现光路层与电路层的垂直互连,通过铜柱填充与绝缘层钝化工艺,将层间信号传输速率提升至10Gbps/μm²,较传统引线键合技术提高8倍。在系统层面,三维集成允许将光放大器、波分复用器等有源器件与MT-FA无源组件集成于同一封装体内,形成光子集成电路(PIC)。例如,在1.6T光模块设计中,通过三维堆叠将8通道MT-FA与硅光调制器阵列垂直集成,使光耦合损耗从3dB降至0.8dB,系统误码率(BER)优化至10⁻¹⁵量级。这种立体化架构还支持动态重构功能,可通过软件定义调整光通道分配,使光模块能适配从100G到1.6T的多种速率场景。随着CPO(共封装光学)技术的演进,三维集成MT-FA芯片正成为实现光子与电子深度融合的重要载体,其每瓦特算力传输成本较传统方案降低55%,为未来10Tbps级光互连提供了技术储备。相比电子通信,三维光子互连芯片具有更低的功耗和更高的能效比。上海光通信三维光子互连芯片厂家直销

相比于传统的二维芯片,三维光子互连芯片在制造成本上更具优势,因为能够实现更高的成品率。光通信三维光子互连芯片生产

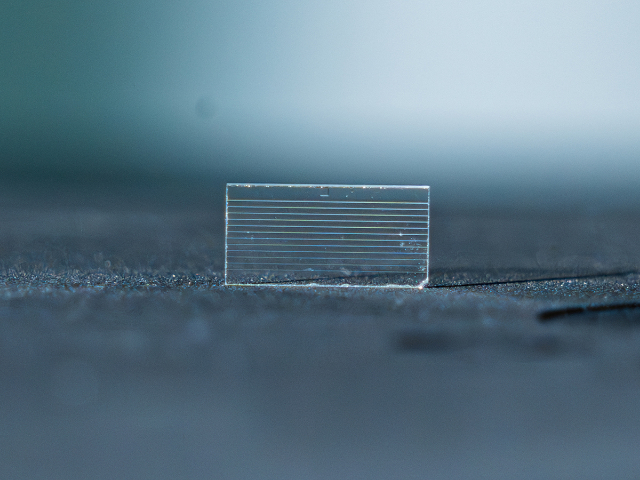

多芯MT-FA光组件作为三维光子集成工艺的重要单元,其技术突破直接推动了高速光通信系统向更高密度、更低损耗的方向演进。该组件通过精密的V形槽基片阵列排布技术,将多根单模或多模光纤以微米级精度固定于硅基或玻璃基底,形成高密度光纤终端阵列。其重要工艺包括42.5°端面研磨与低损耗MT插芯耦合,前者通过全反射原理实现光信号的90°转向传输,后者利用较低损耗材料将插入损耗控制在0.1dB以下。在三维集成场景中,多芯MT-FA与硅光芯片、CPO共封装光学模块深度融合,通过垂直堆叠技术将光引擎与电芯片的间距压缩至百微米级,明显缩短光互连路径。例如,在1.6T光模块中,12通道MT-FA阵列可同时承载800Gbps×12的并行信号传输,配合三维层间耦合器实现波导层与光纤层的无缝对接,使系统功耗较传统方案降低30%以上。这种集成方式不仅解决了高速信号传输中的串扰问题,更通过三维空间复用将单模块端口密度提升至传统方案的4倍,为AI算力集群提供了关键的基础设施支持。光通信三维光子互连芯片生产

多芯MT-FA光组件在三维芯片架构中扮演着连接物理层与数据传输层的重要角色。三维芯片通过硅通孔(TS...

【详情】多芯MT-FA光组件在三维芯片集成中扮演着连接光信号与电信号的重要桥梁角色。三维芯片通过硅通孔(TS...

【详情】多芯MT-FA光收发组件在三维光子集成体系中的创新应用,正推动光通信向超高速、低功耗方向加速演进。针...

【详情】高密度多芯MT-FA光组件的三维集成芯片技术,是光通信领域突破传统物理限制的关键路径。该技术通过将多...

【详情】某团队采用低温共烧陶瓷(LTCC)作为中间层,通过弹性模量梯度设计缓解热应力,使80通道三维芯片在-...

【详情】某团队采用低温共烧陶瓷(LTCC)作为中间层,通过弹性模量梯度设计缓解热应力,使80通道三维芯片在-...

【详情】多芯MT-FA光连接器在三维光子互连体系中的技术突破,集中体现在高密度集成与低损耗传输的平衡上。针对...

【详情】三维光子芯片的集成化发展对光连接器提出了前所未有的技术挑战,而多芯MT-FA光连接器凭借其高密度、低...

【详情】多芯MT-FA光组件在三维芯片架构中扮演着光互连重要的角色,其部署直接决定了芯片间数据传输的带宽密度...

【详情】从技术标准化层面看,三维光子芯片多芯MT-FA光互连需建立涵盖设计、制造、测试的全链条规范。在芯片级...

【详情】三维光子芯片的研发正推动光互连技术向更高集成度与更低能耗方向突破。传统光通信系统依赖镜片、晶体等分立...

【详情】从工艺实现层面看,多芯MT-FA的制造涉及超精密加工、光学镀膜、材料科学等多学科交叉技术。其重要工艺...

【详情】