- 品牌

- 克劳德

- 型号

- LPDDR4信号完整性测试

LPDDR4的排列方式和芯片布局具有以下特点:2D排列方式:LPDDR4存储芯片采用2D排列方式,即每个芯片内有多个存储层(Bank),每个存储层内有多个存储页(Page)。通过将多个存储层叠加在一起,从而实现更高的存储密度和容量,提供更大的数据存储能力。分段结构:LPDDR4存储芯片通常被分成多个的区域(Segment),每个区域有自己的地址范围和配置。不同的区域可以操作,具备不同的功能和性能要求。这种分段结构有助于提高内存效率、灵活性和可扩展性。LPDDR4是否支持固件升级和扩展性?LPDDR4信号完整性测试执行标准

LPDDR4信号完整性测试

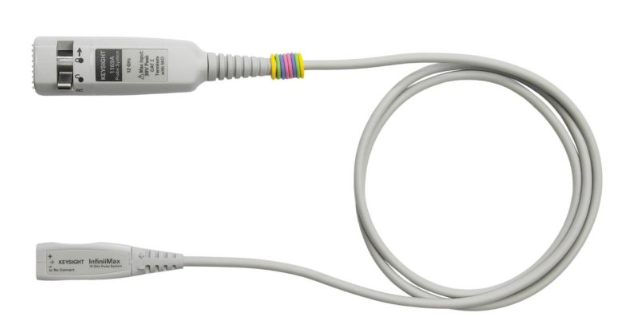

LPDDR4的故障诊断和调试工具可以帮助开发人员进行性能分析、故障排查和系统优化。以下是一些常用的LPDDR4故障诊断和调试工具:信号分析仪(Oscilloscope):信号分析仪可以实时监测和分析LPDDR4总线上的时序波形、电压波形和信号完整性。通过观察和分析波形,可以检测和诊断信号问题,如时钟偏移、噪音干扰等。逻辑分析仪(LogicAnalyzer):逻辑分析仪可以捕捉和分析LPDDR4控制器和存储芯片之间的通信和数据交互过程。它可以帮助诊断和调试命令和数据传输的问题,如错误指令、地址错误等。频谱分析仪(SpectrumAnalyzer):频谱分析仪可以检测和分析LPDDR4总线上的信号频谱分布和频率响应。它可帮助发现和解决频率干扰、谐波等问题,以提高信号质量和系统性能。仿真工具(SimulationTool):仿真工具可模拟LPDDR4系统的行为和性能,帮助研发人员评估和分析不同的系统配置和操作。通过仿真,可以预测和优化LPDDR4性能,验证设计和调试系统。调试器(Debugger):调试器可以与LPDDR4控制器、存储芯片和处理器进行通信,并提供实时的调试和追踪功能。它可以帮助研发人员监视和控制LPDDR4的状态、执行调试命令和观察内部数据,以解决软件和硬件间的问题高速接口LPDDR4信号完整性测试克劳德LPDDR4是否支持高速串行接口(HSI)功能?如何实现数据通信?

LPDDR4采用的数据传输模式是双数据速率(DoubleDataRate,DDR)模式。DDR模式利用上升沿和下降沿两个时钟信号的变化来传输数据,实现了在每个时钟周期内传输两个数据位,从而提高数据传输效率。关于数据交错方式,LPDDR4支持以下两种数据交错模式:Byte-LevelInterleaving(BLI):在BLI模式下,数据被分为多个字节,然后按照字节进行交错排列和传输。每个时钟周期,一个通道(通常是64位)的字节数据被传输到内存总线上。这种交错方式能够提供更高的带宽和数据吞吐量,适用于需要较大带宽的应用场景。

LPDDR4信号架构与测试挑战

LPDDRR4采用双通道16-bit架构,比较高速率4266Mbps,信号完整性测试需关注:·差分时钟(WCK):频率为数据率的1/4,需测试±50ps时序窗口u9666926●数据信号(DQ):单端信号,阻抗需控制在40Ω±10%·命令/地址(CA):比数据速率低50%,但时序要求更严格19666926测试难点:单端信号抗噪能力弱,容限JIN±10%VDDQ(典型值0.6V),需使用20GHz以上示波器捕获微小失真。

关键测试参数与JEDEC标准6926●眼图要求:数据信号眼高≥0.5xVDDQ,眼宽≥0.65UI(@4266Mbps对应153ps)·时序参数:tDQSCK(数据-时钟对齐)误差需<±0.15UI·电源噪声:VDDQ纹波<30mVpp,VDD2(I/O电源)<50mVpp.信号质量:上升时间(20%~80%)<75ps,过冲<15%VDDQ LPDDR4的故障诊断和调试工具有哪些?

对于擦除操作,LPDDR4使用内部自刷新(AutoPrecharge)功能来擦除数据。内部自刷新使得存储芯片可以在特定时机自动执行数据擦除操作,而无需额外的命令和处理。这样有效地减少了擦除时的延迟,并提高了写入性能和效率。尽管LPDDR4具有较快的写入和擦除速度,但在实际应用中,由于硬件和软件的不同配置,可能会存在一定的延迟现象。例如,当系统中同时存在多个存储操作和访问,或者存在复杂的调度和优先级管理,可能会引起一定的写入和擦除延迟。因此,在设计和配置LPDDR4系统时,需要综合考虑存储芯片的性能和规格、系统的需求和使用场景,以及其他相关因素,来确定适当的延迟和性能预期。此外,厂商通常会提供相应的技术规范和设备手册,其中也会详细说明LPDDR4的写入和擦除速度特性。LPDDR4的时钟和时序要求是什么?如何确保精确的数据传输?高速接口LPDDR4信号完整性测试时钟抖动测试

LPDDR4存储器模块在设计和生产过程中需要注意哪些关键要点?LPDDR4信号完整性测试执行标准

LPDDR4可以同时进行读取和写入操作,这是通过内部数据通路的并行操作实现的。以下是一些关键的技术实现并行操作:存储体结构:LPDDR4使用了复杂的存储体结构,通过将存储体划分为多个的子存储体组(bank)来提供并行访问能力。每个子存储体组都有自己的读取和写入引擎,可以同时处理读写请求。地址和命令调度:LPDDR4使用高级的地址和命令调度算法,以确定比较好的读取和写入操作顺序,从而比较大限度地利用并行操作的优势。通过合理分配存取请求的优先级和时间窗口,可以平衡读取和写入操作的需求。数据总线与I/O结构:LPDDR4有多个数据总线和I/O通道,用于并行传输读取和写入的数据。这些通道可以同时传输不同的数据块,从而提高数据的传输效率。LPDDR4信号完整性测试执行标准

LPDDR4的排列方式和芯片布局具有以下特点:2D排列方式:LPDDR4存储芯片采用2D排列方式,即每个芯片内有多个存储层(Bank),每个存储层内有多个存储页(Page)。通过将多个存储层叠加在一起,从而实现更高的存储密度和容量,提供更大的数据存储能力。分段结构:LPDDR4存储芯片通常被分成多个的区域(Segment),每个区域有自己的地址范围和配置。不同的区域可以操作,具备不同的功能和性能要求。这种分段结构有助于提高内存效率、灵活性和可扩展性。LPDDR4支持的密度和容量范围是什么?数字信号LPDDR4信号完整性测试M-PHY测试LPDDR4信号完整性测试LPDDR4是一种低功耗的存储器...

- 测试原理LPDDR4信号完整性测试(SI/PI) 2025-12-20

- 眼图测试LPDDR4信号完整性测试快速出具检测报告 2025-12-19

- 转接板LPDDR4信号完整性测试接口信号案例 2025-12-19

- 夹具测试LPDDR4信号完整性测试系列 2025-12-19

- 物理层数字信号LPDDR4信号完整性测试快速出具检测报告 2025-12-19

- si信号完整性LPDDR4信号完整性测试系列 2025-12-19

- LPDDR4信号完整性测试执行标准 2025-12-19

- 物理层信号完整性测试(SI/PI)LPDDR4信号完整性测试接口测试 2025-12-19

- 校准LPDDR4信号完整性测试时钟抖动测试 2025-12-19

- 高速接口LPDDR4信号完整性测试时钟抖动测试 2025-12-19

- 信息化LPDDR4信号完整性测试RX 2025-01-23

- 自动化LPDDR4信号完整性测试信号完整性测试 2025-01-22

- 智能化多端口矩阵测试LPDDR4信号完整性测试价格优惠 2025-01-22

- 信号完整性测试LPDDR4信号完整性测试测试流程 2025-01-22

- 仪器仪表测试LPDDR4信号完整性测试安装 2025-01-21

- PCI-E测试LPDDR4信号完整性测试技术 2025-01-21

- 甘肃DDR3测试热线 05-10

- 黑龙江USB3.0测试项目 05-10

- DDR测试信号完整性测试价目表 05-10

- 上海DP测试USB测试 05-10

- 设备信号完整性测试价格优惠 05-10

- 福建DDR测试方案商 05-10

- 北京信号完整性测试联系方式 05-10

- 江苏DDR3测试高速信号传输 05-10

- 校准DP测试调试 05-10

- 电气性能测试DDR3测试PCI-E测试 05-10