- 品牌

- 上海伟诺

- 型号

- 伟诺

- 适用行业

- 半导体

- 版本类型

- 网络版

- 语言版本

- 简体中文版

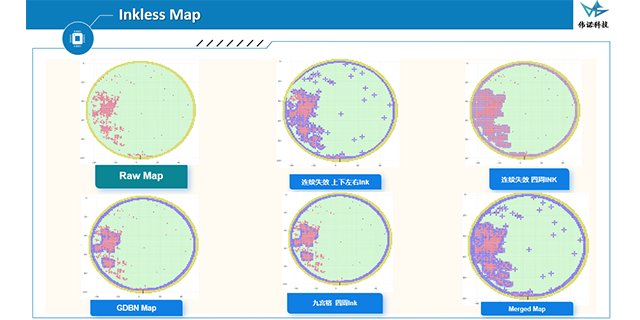

为提升晶圆测试(CP测试)的质量与可靠性,行业的关注点已从单一的电性性能测试,扩展到电性与物理外观并重的综合质量评估。因此,越来越多的公司在CP测试环节中,引入外观检测设备(AOI,AutomatedOpticalInspection),对晶圆上每个Die的表面进行高精度、自动化的扫描与检测,以识别并剔除那些存在裂纹、划痕、污染、崩边或缺损等物理缺陷的不良品。这种做法的价值在于,它弥补了传统电性测试的盲区。一颗芯片可能电性参数测试“通过”,但其物理结构已存在潜在损伤。这类“带伤”的芯片在后续的封装应力或终端应用中有极高早期失效的风险,是产品可靠性的重大隐患。通过AOI检测,可以在晶圆阶段就将这些物理不良品精确拦截。

上海伟诺信息科技有限公司提供专业的AOI与Probe Mapping堆叠方案,解决两大关键问题:一是通过数据融合,筛除外观与电性的全部不良品,生成高可靠性的合一Mapping;二是具备优异的兼容性,可将合并后的Mapping直接转换为各类探针台(如TSK、TEL、UF3000等)可识别的格式,实现从质量判定到生产执行的自动化,有效提升品质与效率。Mapping Over Ink处理强化封测环节质量防线,拦截潜在失效风险Die。北京自动化Mapping Inkless

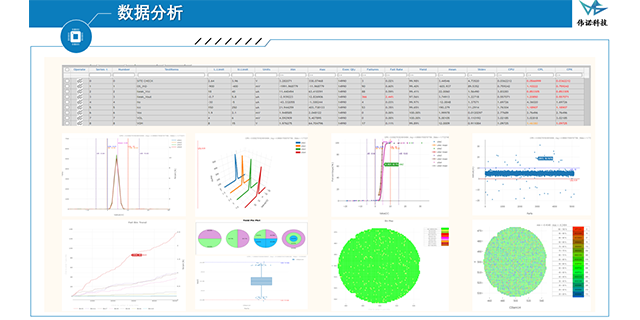

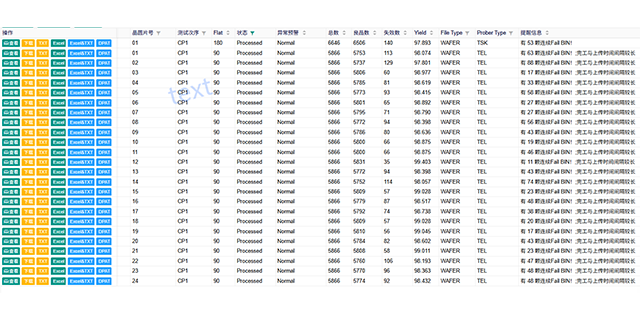

在智能制造转型背景下,YMS已不仅是数据分析工具,更是连接测试与工艺优化的中枢系统。系统实时汇聚来自ETS364、STS8107、93k等平台的测试结果,自动完成结构化清洗与整合,消除信息孤岛。标准化数据库支持动态监控良率变化,例如识别某机台连续三批边缘区域良率偏低,触发设备校准预警。SYL/SBL卡控功能则在指标超限时自动拦截异常批次,防止不良品流入下一环节。报表引擎支持按产品线、客户或班次生成定制化报告,适配不同管理层的信息需求。这种“采集—分析—干预—反馈”的闭环机制,明显提升了生产过程的可控性与响应速度。上海伟诺信息科技有限公司以打造中国半导体软件生态为使命,持续完善YMS的集成能力。西藏半导体PAT上海伟诺信息科技SPAT功能,通过结合测试数据去除超出规范的芯片并生成新的Mapping。

ZPAT 是一种基于统计学的芯片筛选技术,通过在晶圆测试阶段识别并剔除具有潜在缺陷的芯片,从而提升产品的可靠性。在实际的应用过程中需要通过叠加多片Wafer找出在同一坐标下失效的Die的比例,通过特定的算法从而评估其他未失效的Die存在的潜在失效的概率。也是提升芯片质量零缺陷的一种手段。

为助力客户应对日益严苛的“零缺陷”质量挑战,上海伟诺信息科技有限公司将其先进的ZPAT技术深度整合于Mapping Over Ink 解决方案中。这一创新集成赋予用户高度的灵活性与强大的分析能力,使其能够通过一套高度可配置的流程,精确、高效地剔除晶圆上那些性能参数超出统计控制界限的异常芯片,从而构筑起一道基于动态统计过程控制的智能质量防线。

一套高效的良率管理系统开发方案,必须根植于真实生产场景的数据流与决策链。YMS方案覆盖从ETS88、93k、J750等Tester平台自动采集stdf、csv、log等多格式数据,到解析、清洗、整合的完整链路,确保数据源头的完整性与一致性。在此基础上,系统构建标准化数据库,实现对良率信息的统一分类与高效调用。分析层面,方案强调时间序列下的良率波动追踪与晶圆空间维度的缺陷聚类,结合WAT、CP、FT参数变化,形成从现象到根因的完整证据链。SYL与SBL的自动卡控机制嵌入关键控制点,实现预防性质量管理。同时,报表引擎支持按需生成周期报告,并导出为PPT、Excel或PDF,适配不同管理层的信息消费习惯。上海伟诺信息科技有限公司依托多年行业积累,将YMS方案打造为兼具实用性与扩展性的国产选择。Mapping Over Ink处理明显降低早期失效率,减少封装环节的潜在失效风险。

标准化良率管理系统难以覆盖不同企业的工艺路径与管理重点,定制化成为提升系统价值的关键路径。YMS支持根据客户实际使用的测试平台组合、数据结构及分析维度进行功能适配,例如针对特定封装流程优化缺陷分类逻辑,或为高频监控场景开发专属看板。系统底层架构保持统一,上层应用则灵活可调,既保障数据治理规范性,又满足业务个性化需求。定制内容包括但不限于报表模板、卡控阈值、导出格式及用户权限体系,确保系统与现有工作流无缝融合。通过前期深度调研与迭代式交付,定制方案能精确匹配客户在良率提升、异常预警或合规追溯等方面的目标。上海伟诺信息科技有限公司将定制服务视为价值共创过程,以技术灵活性支撑客户业务独特性。Mapping Over Ink处理系统与MES、SPC平台实现数据联动,构建智能化质量管理闭环。新疆MappingOverInk处理系统定制

Mapping Over Ink处理后的数据完整支持回溯为原始Probe格式,满足客户审计需求。北京自动化Mapping Inkless

在半导体制造的后段工艺流程中,对晶圆测试(CP)阶段生成的Mapping图进行PAT(Part Average Testing)处理,已成为一项常规且至关重要的质量管控手段。该技术的价值在于运用统计方法,识别并剔除那些虽未超出规格界限但表现异常的“潜在缺陷”芯片,从而在封装前有效提升产品的良率与可靠性。上海伟诺信息科技有限公司的Mapping Over Ink处理方案,正是这一先进质量理念的践行者。该方案严格遵循AEC-Q100等车规级认证标准,不仅提供标准PAT功能,更针对高可靠性应用的严苛要求,内置了SPAT与DPAT等处理模式。通过对测试参数进行多维度、智能化的异常分析,伟诺方案能有效提升CP测试的缺陷检出率,将早期失效风险遏制在封装之前。这直接带来了测试质量的飞跃与测试成本的优化,助力客户轻松满足车规、工规等产品对质量与可靠性的不懈追求。北京自动化Mapping Inkless

上海伟诺信息科技有限公司在同行业领域中,一直处在一个不断锐意进取,不断制造创新的市场高度,多年以来致力于发展富有创新价值理念的产品标准,在上海市等地区的数码、电脑中始终保持良好的商业口碑,成绩让我们喜悦,但不会让我们止步,残酷的市场磨炼了我们坚强不屈的意志,和谐温馨的工作环境,富有营养的公司土壤滋养着我们不断开拓创新,勇于进取的无限潜力,携手大家一起走向共同辉煌的未来,回首过去,我们不会因为取得了一点点成绩而沾沾自喜,相反的是面对竞争越来越激烈的市场氛围,我们更要明确自己的不足,做好迎接新挑战的准备,要不畏困难,激流勇进,以一个更崭新的精神面貌迎接大家,共同走向辉煌回来!

- 中国澳门可视化MappingOverInk处理平台 2026-01-30

- 陕西晶圆Mapping Inkless系统价格 2026-01-30

- 中国台湾自动化GDBC系统定制 2026-01-29

- 上海可视化PAT服务 2026-01-29

- 北京自动化Mapping Inkless 2026-01-29

- 浙江自动化GDBC解决方案 2026-01-29

- 中国台湾可视化MappingOverInk处理工具 2026-01-29

- 云南晶圆GDBC系统价格 2026-01-29